Storage Developer Conference September 22-23, 2020

# **Emerging Data-centric Storage Architectures**

Pankaj Mehra, Ph.D. VP Storage Pathfinding Samsung Semiconductor Inc.

## Challenges of Data@Scale

### Bottlenecks

Processing power and processing bandwidth

Metadata inefficiency of object storage & retrieval

Wire protocol termination for disaggregated flash

### Inefficiencies

Inability to deliver both performance and scale

Wasted endurance

Wasted memory BW

CPU overhead of I/O

CPU overhead of I/O virtualization

## SD@

## Good Ideas, Already In-Play

- Virtualization offload

- SMRDB (since HDD days)

- DB filtering acceleration

- Storage NWconv (since FC)

- Active Disk (since HDD days)

- OSD (since HDD days)

#### Why Revisit?

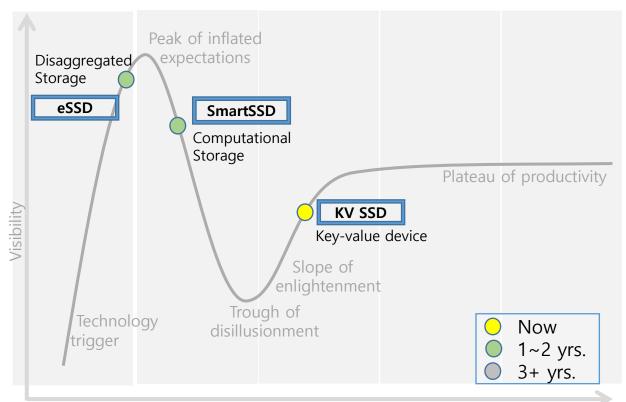

Because in 2020, three distinct 25-y.o. ideas meet the SSD!

## SD@

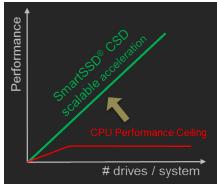

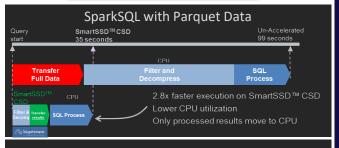

#### SmartSSD® CSD Scales to Accelerate Data-Rich Workloads

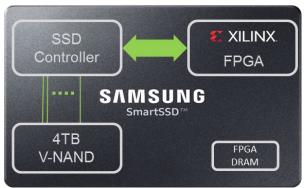

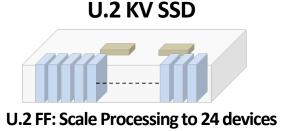

#### SmartSSD U.2 Platform

#### Acceleration Concept

#### **Partner Solutions**

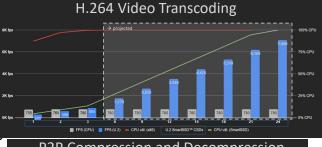

#### P2P Compression and Decompression (MB/s/cpu) Eff. 1.72 1.42 Compression: 2.85 2173 2173 NoLoad-CSD Compression: 2.85 2862 2938 1.01 0.06 NoLoad-CSD w/ p2pdma 2.85 1823 2989 1.71 1.81 Not pad-CSD 2.85 2022 3690 1.01 0.14

NoLoad-CSD w/ p2pdma

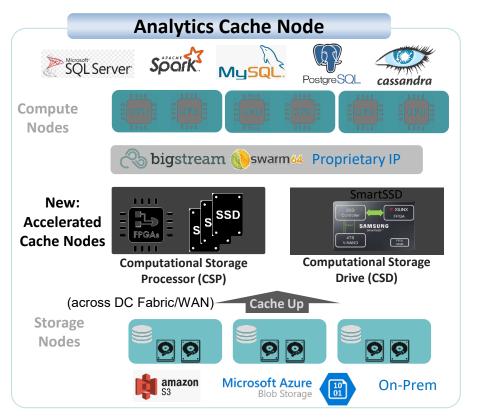

#### **Computational Storage**

- √ 3 & 6 GBps internal BW per device: Minimize external data movement

- ✓ FPGA: Each device has 3x~10x core equivalents for offload/acceleration

- √ 4TB storage, 4 GB FPGA DRAM:

For Inline and Data@Rest processing

#### **Scalable Performance**

- ✓ Near Data Processing: Data form conversion, Filtering, Metadata management, DB Analytics, Vide processing

- New Services: Secure content, Edg acceleration

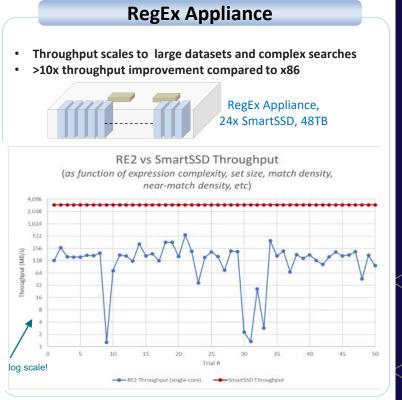

## **Computational Storage Use Cases Examples**

3<sup>rd</sup> party and proprietary acceleration stacks run on Computational Storage to accelerate real-time analytics and regex searches for cybersecurity

SD®

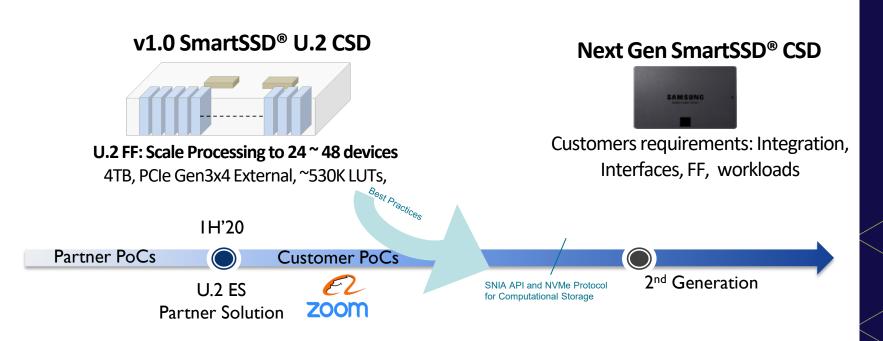

## Samsung SmartSSD® Technology Roadmap

SD@

- Samples, development tools, partners solutions available for immediate PoC

- Customer PoC Test&Dev systems/support available from Samsung and partners

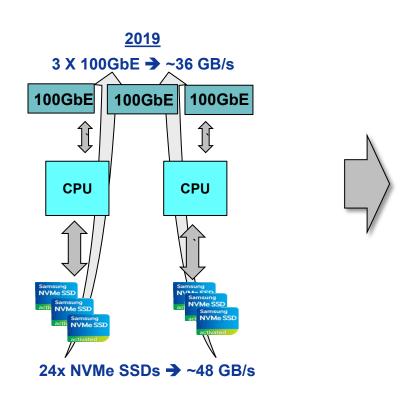

## **Ethernet SSD targets IO bottleneck in Storage Chasses**

CPU and IO bottleneck for storage throughput performance

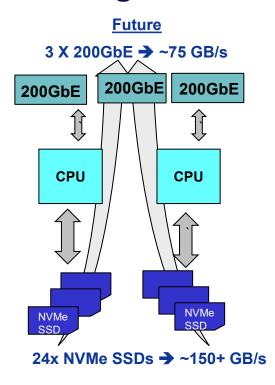

### **NVMe-oF SSD based EBOF**

NVMe-oF EBOF can address bandwidth, scalability, and flexibility

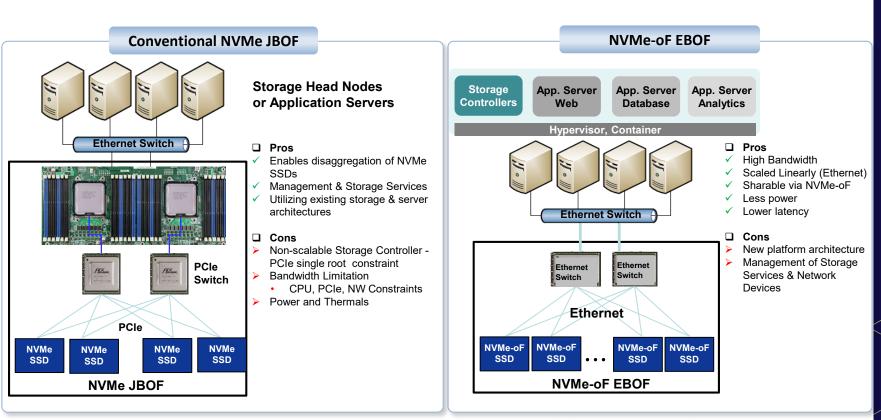

## Samsung Ethernet SSD Technology Roadmap

- SD@

- Samples, development tools, partners solutions available for immediate PoC

- Customer PoC Test&Dev systems/support available from Samsung and partner

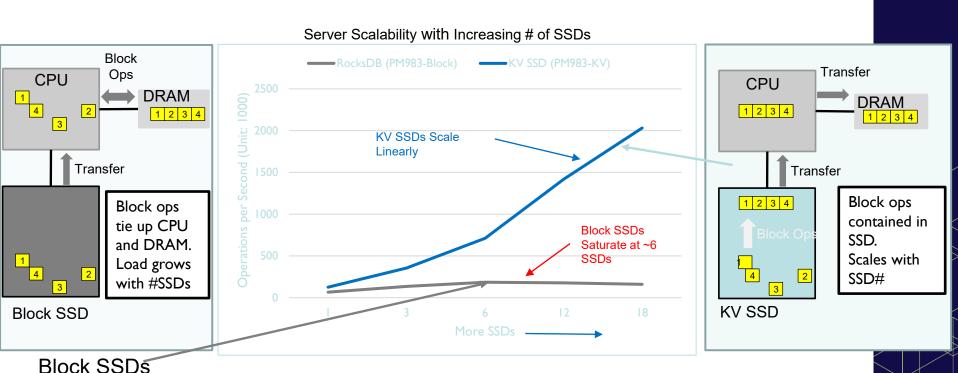

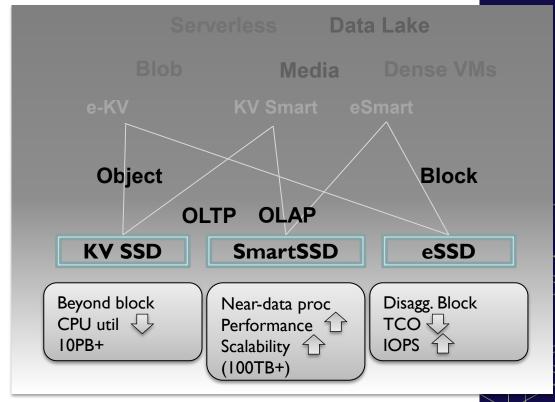

## **KV SSD** is about Efficient Block Operations

SD@

Block operations on CPUs ⇒ Bottlenecks, Scaling Inefficiency. KV SSD offloads Block operations from CPUs.

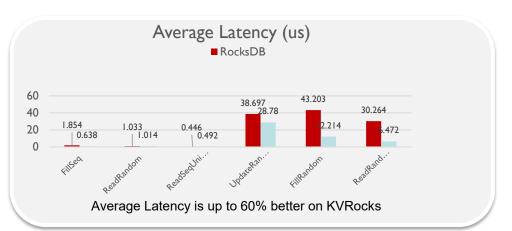

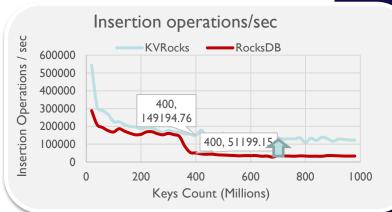

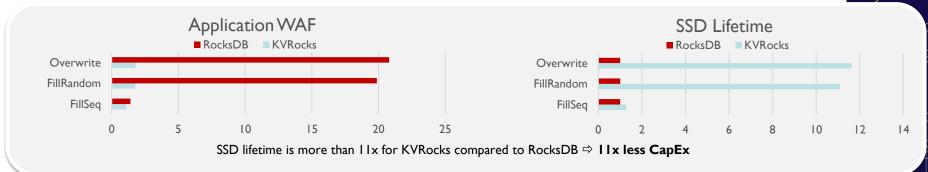

## **KV-optimized SW shows Multiple Efficiency Benefits**

## Samsung KV SSD Technology Roadmap

SD@

Stack open sourced at <a href="https://github.com/OpenMPDK/KVSSD">https://github.com/OpenMPDK/KVSSD</a>

4TB, PCle Gen3x4 External

**Next Gen KV SSD**

Your requirements? (Integration, Interfaces, FF, Workloads)

1H'20

Software dev

Partner Testing

Rocks DB repl. KVCeph

Partner Solution

2<sup>nd</sup> Generation

Minio

## Benefits Summary

|                               | SmartSSD | Ethernet<br>SSD | Key-Value<br>SSD | Zoned<br>Name<br>Spaces |

|-------------------------------|----------|-----------------|------------------|-------------------------|

| Application Awareness         | ✓        |                 | ✓                | ✓                       |

| Acceleration                  | ✓        |                 |                  |                         |

| Reduce data-related CPU load  | ✓        |                 | ✓                |                         |

| Improved Write Endurance      |          |                 | ✓                | ✓                       |

| Fewer protocol terminations   | ✓        | ✓               |                  |                         |

| Min device virtualization o/h |          |                 |                  | ✓                       |

| Fewer stack translations      |          | ✓               | ✓                |                         |

| Metadata Optimization         |          |                 | ✓                |                         |

| Scaling Data Bandwidth        | ✓        |                 |                  |                         |

| Saving L2-to-Memory BW        | ✓        |                 | ✓                |                         |

| Control@Scale (IODT, QoS)     |          |                 |                  | ✓                       |

| Maximize #SSDs/chassis        | ✓        | ✓               | ✓                | ✓                       |

## Possible Convergence

| Host<br>Interface | Addressing | Accelerator |  |

|-------------------|------------|-------------|--|

| PCle              | Block      | None        |  |

| Ethernet          | ZNS        | FPGA        |  |

|                   | Key-Value  |             |  |

Please take a moment to rate this session.

Your feedback matters to us.

- Bullet one

- Bullet two

- Bullet 3

- Bullet 4

## Dr. Pankaj Mehra

Vice President, Storage Pathfinding

Samsung Semiconductor Inc.

- Subhead

- Example 1

- Example 2

- Subhead