STORAGE DEVELOPER CONFERENCE

Virtual Conference September 28-29, 2021

# Emerging Computer Architectures Powered by Emerging Memories

Change Is Upon Us!

Jim Handy, Objective Analysis Tom Coughlin, Coughlin Associates A SNIA, Event

### Outline

- Emerging Memory Status

- Using Emerging Memories in Computing

- Changes to Computer Architecture

- A Path to the Future

- Q & A

# **Emerging Memory Status**

What's Here Now, and What's Coming

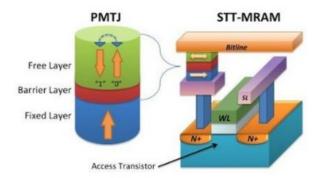

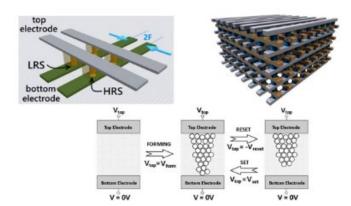

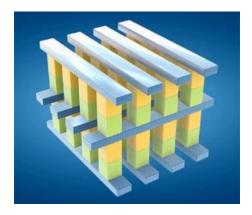

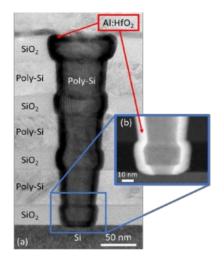

### Emerging Memory Cast of Characters MRAM PCM/XPoint

**ReRAM**

4 | ©2021 Storage Networking Industry Association. ©2021 Objective Analysis & Coughlin Assoc. All Rights Reserved.

**FRAM**

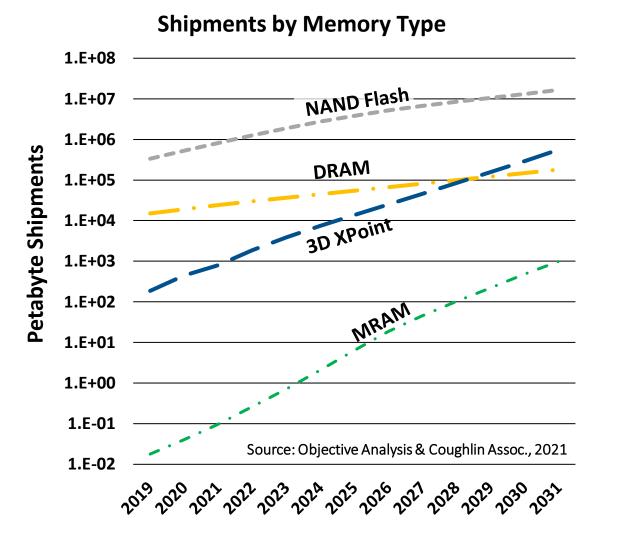

### PM Is Real, and Getting Realer!

- DRAM & NAND have staying power

- 3D XPoint poised to make serious inroads

- MRAM is doing well today

- Also gaining acceptance as embedded memory in SoCs

- This outlook is anything <u>but</u> certain!

### All Emerging Memories Have Similarities

#### Persistent

#### Slower than DRAM, faster than NAND Flash

- No erase-before-write

- Read & write speeds much more similar than in NAND

- Promise to scale beyond DRAM & NAND flash

- Will extend Moore's Law price reductions

- Suffer from economies of scale disadvantage

- If it's cheap it will sell in volume

- If it sells in volume it will become cheap

### New Report: Emerging Memories Take Off!

#### **Now Available!** <u>https://Objective-Analysis.com/reports/#Emerging</u> http://www.tomcoughlin.com/techpapers.htm

STORAGE DEVELOPER CONFERENCE

# Using Emerging Memories in Computing

Are We Causing Problems for Ourselves?

### Eventually, Persistence Will Be Everywhere! Persistent Persistent CPU Memory Registers Persistent Storage Cache Persistent

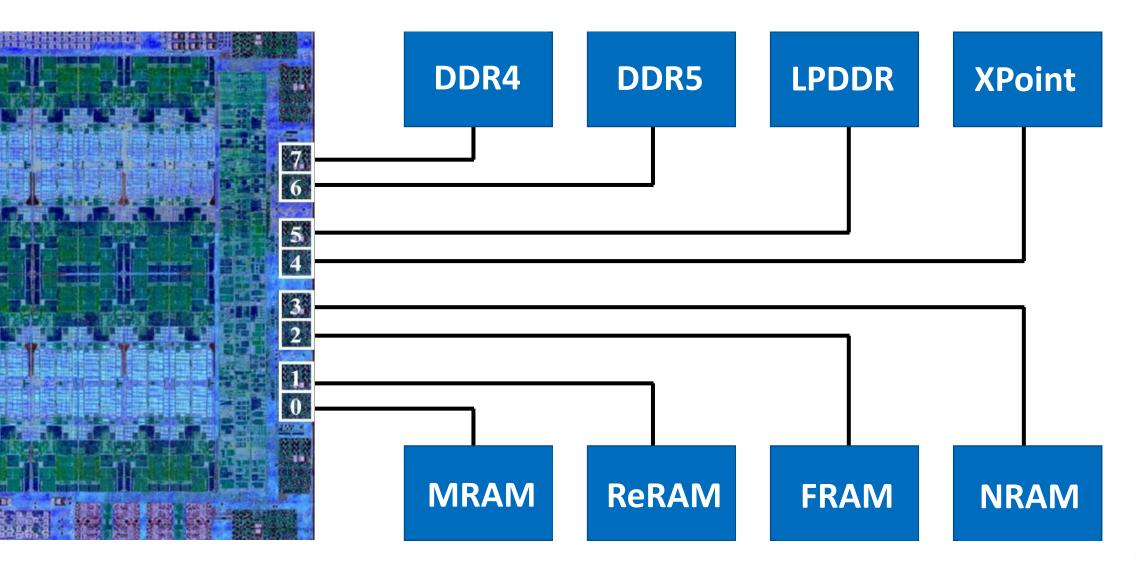

### **DDR** Issues

#### Doesn't support mixed memory speeds

- XPoint slower than DRAM

- Writes slower than reads

#### The DRAM controller is within the CPU

- The most expensive real estate in the world

- Persistence complicates it

#### Decreasing number of DIMMs per channel

- Capacitance issues

- Undermines bandwidth & capacity needs

- Consumes massive power & pins

### Software Issues

#### Memory is Memory & Storage is Storage

- ...and never the twain shall meet!

- Code must be rewritten to gain most of the advantage

- This takes time

#### Cache considerations

Persistent & non-persistent flushes

#### Security needs to be thought through

- Power-off doesn't mean data is lost

- New path to physical data theft

# **Changes to Computer Architecture**

Solving Those Problems

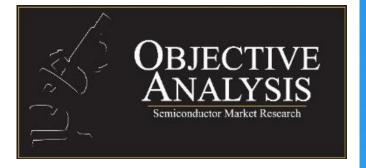

### Far Memory Supports Mixed Access Speeds

- I look at yours, you look at mine

- Yours is slow to me, mine is slow to you

- Data sharing is enormously fast!

### **OMI Brings That Concept to Near Memory**

STORAGE DEVELOPER CONFERENCE

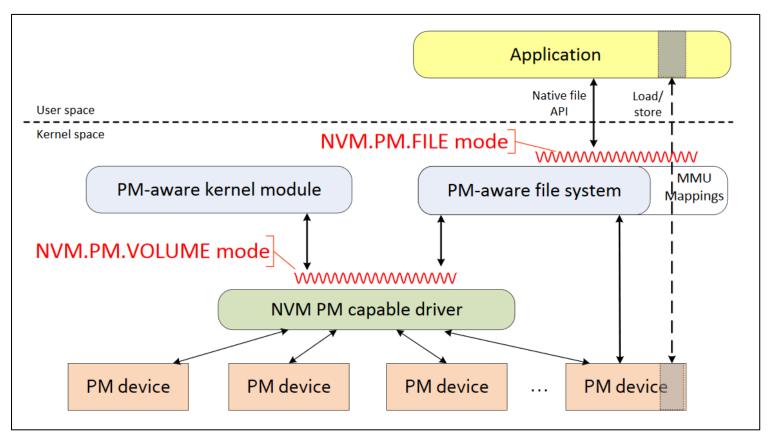

### **SNIA NVM Programming Model**

#### Supporting software now available

Intel, SAP, Oracle, who else?

### **Intel Support**

#### App Direct Mode

- Harnesses Optane's persistence

- Uses SNIA NVM Programming Model

#### Memory Mode

- Not persistent

- Just like a big huge DRAM

#### Special IA instructions

Manages cache into PM

# A Path to the Future

Tomorrow's Computing Architectures

### Putting Together the Pieces

### Q&A Who's Still Awake?

## Please take a moment to rate this session.

Your feedback is important to us.

20 | ©2021 Storage Networking Industry Association. All Rights Reserved.